Embedded World, which was held this week in Nuremberg, Germany, lacks the glamor and headlines of next week’s Mobile World Congress in Barcelona. Yet, along with showing off the usual circuit boards, the show coincided with the debut of two interesting new system-on-chips that combine Linux-friendly ARM Cortex-A cores with microcontroller units (MCUs).

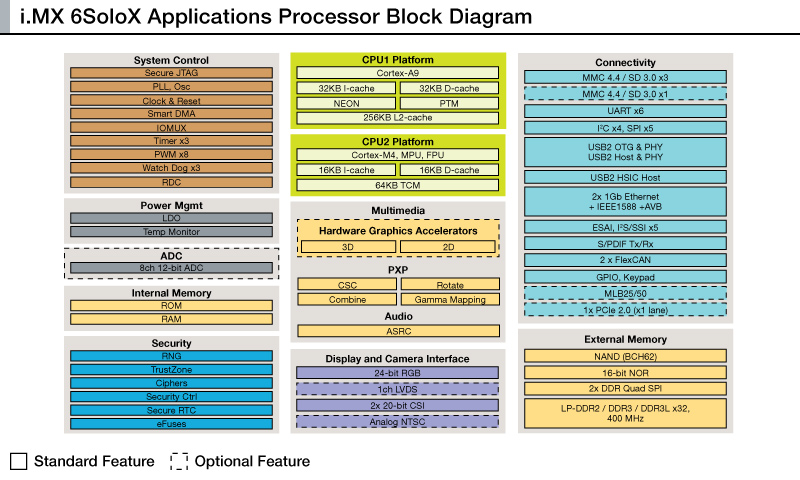

On the low end, angling for the Internet of Things market, is Freescale’s i.MX6 SoloX, which combines a version of the single-core Cortex-A9-based i.MX6 Solo SoC with a Cortex-M4 MCU.

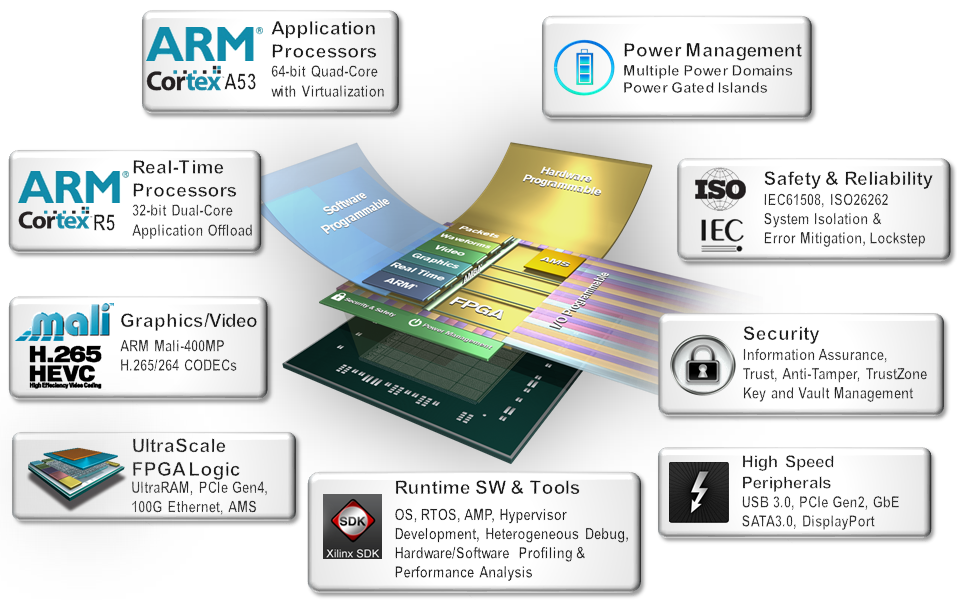

On the high end is a next-generation Xilinx Zynq SoC called the Zynq UltraScale+ MPSoC. The already hybrid ARM/FPGA Zynq SoC moves to a cutting edge 16nm 3D FinFet process, switches its dual Cortex-A9 cores to four Cortex-A53s, boosts the power of its FPGA, and adds a pair of Cortex-R5 MCUs for better real-time processing.

MCUs are a large and growing business for ARM, showing up in industrial equipment, robots, sensor systems, and all manner of low-end embedded gizmos. Yet, these real-time oriented chips exist mostly beyond the reach of advanced operating systems like Linux. Many of the hugely popular Cortex-M MCUs and the less commonly seen Cortex-R chips can run the stripped-down uClinux, with some tradeoffs, but even lightweight brands of full-fledged Linux distros, such as OpenWRT, cannot tap these devices.

Instead, MCUs typically run real-time operating systems (RTOSes) such as ARM’s new Mbed OS, which is designed for IoT applications on the Cortex-M. ARM is also working on an automotive-focused ARMv8-R version of the Cortex-R that will be able to run lightweight Linux distros.

Meanwhile, Linux itself continues to gain real-time chops thanks to continuing PREEMPT_RT patches, but the minimum processor requirements for Linux mean that many real-time tasks are beyond its purview.

Freescale i.MX6 SoloX

Freescale previously experimented with a hybrid Cortex-A/Cortex-M SoC in its Vybrid-F, which combined a Cortex-A5 core running Linux with a Cortex-M4 microcontroller running Freescale’s MQX RTOS.

Now, it’s adding a similar MQX-running Cortex-M4 to its popular Cortex-A9-based i.MX6 processor family with the Freescale i.MX6 SoloX.

The i.MX6 has been popular among embedded SBC and computer-on-module vendors, in part due to its low power consumption, multimedia accelerators, and customizable core configurations. You can choose between single, dual, and quad-core versions, and the Solo and Dual versions each come with different flavors of Vivante graphics processing units (GPUs). The Linux- and Android-ready i.MX6 has appeared in numerous community-backed hacker SBCs, including the HummingBoard, LinkSprite Acadia, RIoTboard, Udoo Quad, WandBoard, and Warpboard.

The SoloX takes a 1GHz Cortex-A9 Solo core and combines it with a Cortex-M4 in order to offer “deterministic, real-time responsiveness,” says Freescale. But unlike the Vybrid, it also features a configurable resource domain controller to better coordinate the different cores. The technology allows peripherals to be locked or shared by the CPU cores.

The SoC’s discrete CPU core power domains also enable independent power state control and low current draw, including the ability to turn off the Cortex-A9 core, even while the Cortex-M4 performs low-level system monitoring tasks. Other new features include cryptography and dual-port gigabit Ethernet audio video bridging (AVB) for improved quality-of-service, thereby overcoming the SoCs earlier GbE throughput limitations.

The new features are particularly targeted at automotive gear. However, combining a single Cortex-A9 core with an MCU lends itself to a wide variety of low-power IoT applications ranging from home automation to robotics.

Xilinx Zynq UltraScale+ MPSoC

This week’s UltraScale+ announcements were big news in the FPGA (field programmable gate array) world where Xilinx and Altera leapfrog each other for bragging rights. Xilinx is now back on top with the UltraScale+, which advances from the previous 28nm and 20nm fabrication process used by the company’s flagship FPGAs and Linux-ready “Zynq” ARM/FPGA hybrid SoCs, to a cutting-edge 16nm FinFet process. This is essentially the same process that will be used by upcoming, 2.5GHz Cortex-A72 processors. The UltraScale+ process is touted for adding 3D packaging technology in addition to the 3D FinFet transistors, resulting in so called “3D-on-3D” technology.

In addition to the claimed two to five times greater system-level performance/watt gained from the new fab process, UltraScale+ processors are notable for “UltraRAM,” a new type of memory block that provides much more on-chip capacity with improved performance and reduced latency. New SmartConnect interconnects, meanwhile, let hardware designers optimize each interconnection between processing blocks rather than apply a one-size-fits-all approach, says Xilinx. Other enhancements include DDR4 support, high-speed memory cascading, enhanced DSP slices with 27×18-bit multipliers and dual adders, and more.

The UltraScale+ treatment is being given to Xilinx’ Kintex and Virtex FPGAs, as well as the Linux-ready Zynq, which EEJournal called out as the most improved of the UltraScale+ SoCs. The original Zynq was just as groundbreaking, in that it combined Cortex-A9 and FPGA subsystems on a single die, linking them via a high-speed AXI4 interconnect. This helped integrate processing in ways that were impossible with earlier combo chipsets, and opened up much of the FPGA fabric to Linux developers and C programmers, who are far more numerous than FPGA specialists.

The Zynq UltraScale+ MPSoC combines the above listed UltraScale+ enhancements with a boost from two Cortex-A9 to four 64-bit Cortex-A53 cores. As before, it also integrates FPGA circuitry of various levels, depending on the model. In this case, however, the higher-end versions offer up to 914 logic cells, over twice the maximum of the previous versions.

The Zynq UltraScale+ also adds dual Cortex-R5 microcontrollers clocked at up to 600MHz for greater real-time processing, making this a triple hybrid SoC. If you count the new Mali-400MP GPU and optional, hardened H.265/264 video processing unit, up to five unique species of processors are involved. Power management and security chips are also available. All these cores are tied together with the new SmartConnect, as well as new “heterogeneous multi-processing” features, “basically expanding the ARM-based processing system with a lot of optimized hard IP,” according to EEJournal.

The new Zynq SoC are supported with the Xilinx PetaLinux distribution, SDK, and board support package. It appears that Linux, rather than a separate RTOS, can be used to tap the capabilities of the dual Cortex-R5 MCUs. The BSP includes device drivers for the SoC’s embedded processing IP cores, kernel, and boot loader configurations, enabling “software engineers to focus on their value-added applications rather than low level development tasks,” says Xilinx.

Early access to the UltraScale+ processors starts in the second quarter, with samples coming later this year, and volume production slated for 2016. The Freescale i.MX6 SoloX, meanwhile, is available now.